Zilog Z80

Info

This processor was built after a project that lasted two years of hard work. It was created by Federico Faggin after facing the development of a new processor that was cheaper and compatible with the Intel 8080, but that was better in performance.

This Little-endian 8-bit processor was launched on the market in July 1976, offering a cheap price and facing the already famous Intel 8080 at that time. Its compatibility with the 8080 meant that the applications developed for this Intel processor could be run on the Z80, including the CP/M operating system.

The Z80 with respect to the Intel 8080 presented some improvements making the Z80 be considered as an extension of the Intel. The Z80 featured an expanded instruction system, the inclusion of a couple of new registers or the simplification of the necessary auxiliary devices (clock, memory, etc). It hit the market with quite a bit of force, sweeping the Intel 8080.

This processor is considered as a hybrid between the accumulator architecture and the general purpose register architecture. It could be included within the register-memory type processors.

General characteristics

The Z80 has an 8-bit data bus, but it handles 16-bit instructions and addresses (so it could address up to 64 Kb). Alignment is not required. It has 22 registers (18 of 8 bits, and 4 of 16 bits). 12 of them can be used in pairs (so we would have 6 16-bit registers). The clock frequency is variable depending on the version. It started with a 2.5 MHz clock cycle, with later models reaching 20 MHz. The Z80A, the popular version ran at 3.58 MHz (4 MHz from the factory). It has 6 different addressing modes.

Records

- A is the accumulator register, B,C,D,E,H and L are 8-bit general registers. They can form pairs (BC, DE, HL) of 16 bits

- A',B',C',D`,E',H`y L' (alternate bank), replica of original register bank.

- I (Stores top of interrupt vector table start address).

- R (Store memory block to refresh).

- F (Stores condition bits).

- IX, IY (Index Records).

- SP (stack pointer).

- PC (Program Counter).

- F (Register of condition bits): Adds H (indicates if the result has been carried from the bottom to the top) and P (parity bit).

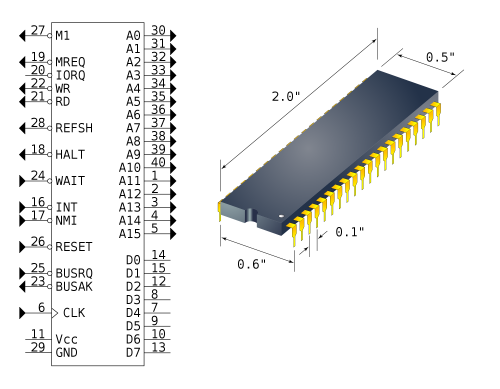

Connection diagram